IBM研發共封裝光學技術,加速AI模型訓練

前言:

新的光電共封裝技術或取代數據中心中的電互連裝置,大幅提高AI和其他計算應用的速度與能效。

作者| 方文三

圖片來源|網 絡

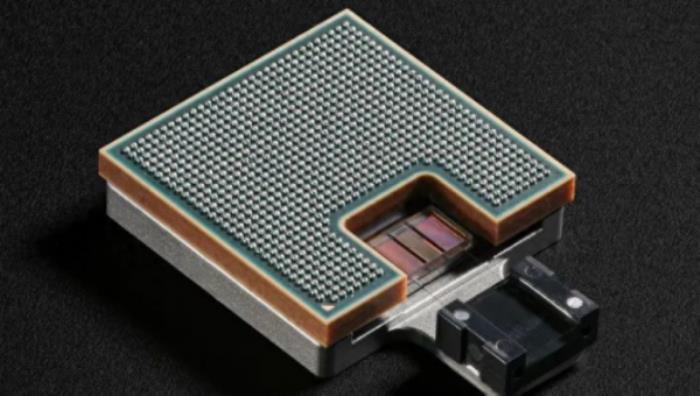

IBM新型的共封裝光學技術

近日,IBM宣布了一項重大的光學技術突破,該技術可以以光速訓練AI模型,同時節省大量能源。

IBM發布的技術論文顯示,這項技術是一種新型的共封裝光學技術(co-packaged optics),可以利用光速實現數據中心內部的連接,從而替代目前使用的銅電纜。

盡管光纖技術已在全球商業和通信中廣泛應用,但大多數數據中心內部仍依賴于銅電纜進行短距離通訊。這導致GPU加速器在訓練過程中常常處于閑置狀態,浪費大量的時間和能源。

因此IBM的研究團隊展示了如何將光的速度和容量引入數據中心,顯著提高數據中心的通信帶寬,減少GPU的閑置時間,從而加速AI模型的處理速度。

共封裝光學技術的核心理念

共封裝光學技術,是將激光器、調制器、光電探測器等光學元件與電子元件共同封裝在一個芯片內。這種技術不僅提高了產品的集成度和可靠性,還顯著降低了系統成本和復雜度。

通過光纖連接,CPO芯片能夠實現高速、高效的光學傳輸和處理,從而大幅提升系統性能。

事實上,CPO并不是最近才有的新技術。早在一年前,臺積電就攜手博通、英偉達等大客戶共同推進這項技術的研發進度,制程技術從45nm延伸到7nm,原計劃2024年就開始迎來大單,并在2025年左右達到放量階段。

比現有芯片間通信帶寬快80倍

得益于近年來芯片技術的飛速發展,芯片上能夠容納更多、更密集的晶體管。以IBM的2納米芯片技術為例,其可在單一芯片上植入500多億個晶體管。

在這樣的技術基礎上,光電共封裝技術致力于擴大加速器之間的互連密度,幫助芯片制造商在電子模組上添加連接芯片的光通路,從而突破現有電子通路的帶寬限制。

IBM所研發的新型高帶寬密度光學結構以及相關創新成果,通過每個光通道傳輸多個波長,有望將芯片間的通信帶寬提升至電線連接的80倍。

增加光纖連接數量

與目前最先進的光電共封裝技術相比,IBM的創新成果使芯片制造商能夠在硅光子芯片邊緣增加六倍數量的光纖,即所謂的“鬢發密度 (beachfront density)”。

每根光纖寬度約為頭發絲的三倍,長度從幾厘米到幾百米不等,卻可傳輸每秒萬億比特級別的數據。

這意味著數據中心內部的數據傳輸能力將得到極大提升,為大規模數據的快速處理提供了有力支持。

通過嚴格測試確保穩定性

IBM團隊采用標準封裝工藝,在50微米間距的光通道上封裝高密度的聚合物光波導 (PWG),并與硅光子波導絕熱耦合。

尤為值得一提的是,此次光電共封裝模塊采用50微米間距的聚合物光波導,首次成功通過了制造所需的所有壓力測試。

這些測試涵蓋高濕度環境、-40°C至125°C的極端溫度以及機械耐久性測試,確保了光互連裝置即使在彎曲等復雜情況下,也不會出現斷裂或數據丟失的問題,為該技術在實際數據中心環境中的可靠應用提供了堅實保障。

原理簡單實際推廣上難度并不小

這種所謂的“硅光芯片”,是在硅的平臺上,將傳統芯片中的電晶體替換成光電元件,進行電與光訊號的傳導。對比傳統芯片會出現電訊號的丟失與耗損的情況,光訊號不僅損耗少,還實現更高頻寬和更快速度的數據處理。

首先,硅光產品并沒有到大規模需求階段。雖說有自動駕駛和數據中心兩大領域的需求,但目前還沒有主流芯片廠商推出高性能芯片。

其次,硅光產品需要考慮相對高昂的成本問題。受限于大量光學器件,一個硅光器件需要采用各種材料,在缺乏大規模需求的情況下,硅光產品成為一種“高價、低性價比”的產品。同時,器件的性能與良品率難以得到保障。

最后,硅光芯片在打通各個環節還需要努力。例如設計環節,雖然已經有EDA工具支持,但算不上專用;而在制造與封裝環節,類似臺積電、三星等大型晶圓代工廠都沒有提供硅光工藝晶圓代工服務。

即便是已經推出COUPE技術的臺積電,短時間內會專注更加成熟的封裝方案,很難勻出產能提供給硅光芯片。

結尾:

面對日益增長的 AI 性能需求,光電共封裝技術開創了一條新的通信途徑,并可能取代從電子到光學的模塊外通信,這一技術突破延續了IBM 在半導體創新方面的領導地位。

內容來源于:美通社:IBM 發布光學技術關鍵突破,生成式AI迎來"光速時代";鎂客網:IBM官宣全新光學技術,用光也能訓練AI?

原文標題:AI芯天下丨趨勢丨IBM研發共封裝光學技術,加速AI模型訓練

- 免責聲明

- 本文所包含的觀點僅代表作者個人看法,不代表新火種的觀點。在新火種上獲取的所有信息均不應被視為投資建議。新火種對本文可能提及或鏈接的任何項目不表示認可。 交易和投資涉及高風險,讀者在采取與本文內容相關的任何行動之前,請務必進行充分的盡職調查。最終的決策應該基于您自己的獨立判斷。新火種不對因依賴本文觀點而產生的任何金錢損失負任何責任。

新火種

2024-12-25

新火種

2024-12-25